Icemos Technology Ltd Product Specification 1900.673502 Issue Date 07 May 2021 14:42:5

| Part Number | Customer |

|-------------|----------|

|             |          |

| Category      | Parameter |                                                 | Specification                     | Measurement Method          |

|---------------|-----------|-------------------------------------------------|-----------------------------------|-----------------------------|

| OverallWafer  | 1.0       | Diameter                                        | 100.00 +/- 0.20 mm                |                             |

|               | 2.0       | Primary Flat Orientation                        | {110} +/- 1.0 degree              | Wafer Vendor                |

|               | 3.0       | Primary Flat Length                             | 32.50 +/- 2.50 mm                 | Wafer Vendor                |

|               | 4.0       | Secondary Flat Orientation                      | none                              | Wafer Vendor                |

|               | 5.0       | Overall Thickness                               | 501.00 +/- 11.00 μm               | ADE, 100%                   |

|               | 6.0       | Total Thickness Variation (TTV)                 | <5.00μm                           | Guaranteed by Process       |

|               | 7.0       | Bow                                             | <80.00μm                          | ADE to ASTM F534, 100%      |

|               | 8.0       | Warp                                            | <80.00μm                          |                             |

|               | 9.0       | Edge Chips                                      | 0                                 | Bright Light, 100% (note 2) |

|               | 10.0      | Edge Exclusion                                  | 5mm                               |                             |

| HandleSilicon | 11.0      | Handle Growth Method                            | CZ                                | Wafer Vendor                |

|               | 12.0      | Handle Orientation                              | {100} +/- 1.0 degree              | Wafer Vendor                |

|               | 13.0      | Handle Thickness                                | 350.00 +/- 10.00 μm               | ADE, 100%                   |

|               | 14.0      | Handle Doping Type                              | P                                 | Wafer Vendor                |

|               | 15.0      | Handle Dopant                                   | Boron                             | Wafer Vendor                |

|               | 16.0      | Handle Resistivity                              | 1 - 30 Ohmcm                      | Wafer Vendor                |

|               | 17.0      | Backside Finish                                 | Polished with Oxide and Lasermark | Guaranteed by process       |

| BuriedOxide   | 18.0      | Oxide Type                                      | Thermal                           |                             |

|               | 19.0      | Oxide Thickness                                 | 10,000.00 +/- 500.00 A            | Nanospec centre point, 4%   |

|               | 20.0      | Oxide formed on                                 | Handle and / or Device wafer      | Graranteed by process       |

| DeviceSilicon | 21.0      | Device Growth Method                            | CZ                                | Wafer Vendor                |

|               | 22.0      | Device Orientation                              | {100} +/- 1.0 degree              | Wafer Vendor                |

|               | 23.0      | Nominal Thickness                               | 148.00 +/- 2.00 μm                | Filmetrics 9pt, 100%        |

|               | 24.0      | Distance to device silicon edge from wafer edge | < 2.0 mm                          | Guaranteed by process       |

|               | 25.0      | Depth into handle variation within wafer        | < 100um                           | Guaranteed by process       |

|               | 26.0      | Device Doping Type                              | P                                 | Wafer Vendor                |

|               | 27.0      | Device Dopant                                   | Boron                             | Wafer Vendor                |

|               | 28.0      | Device Resistivity                              | 1 ~ 30 Ohm cm                     | Wafer Vendor                |

|               | 29.0      | Voids                                           | none                              | Bright Light, 100% (note 2) |

|               | 30.0      | Scratches                                       | 0                                 | Bright Light, 100% (note 2) |

|               | 31.0      | Haze                                            | none                              | Bright Light, 100% (note 2) |

|               | 32.0      | LPD Count                                       | < 30 > 0.3um                      | Tencor Particle counter     |

Page 1 of 2 14/05/2021 www.icemostech.com

| Part Number       |                      | Customer                                                                                |                       |

|-------------------|----------------------|-----------------------------------------------------------------------------------------|-----------------------|

| Category          | Parameter            | Specification                                                                           | Measurement Method    |

| Shipping Details  | Wafer per box :      | Max 25                                                                                  |                       |

|                   | Packaging:           | Taped Polypropylene Wafer Box<br>Empak, Ultrapak, 100.00mm<br>Antistatic Double Bagging |                       |

|                   | Lot Shipment Data    | Device Thickness Bow / Warp Data Handle and SOI Thickness                               |                       |

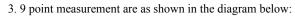

| Explanatory Notes | 1. Microscope inspec | tion performed using microscope scan as below. 5x objective.                            |                       |

|                   |                      | pections performed exclude all wafer area outside the edge exclusio                     | on defined in Overall |

2. All bright light inspections performed exclude all wafer area outside the edge exclusion defined in Overall Wafer, Edge Exclusion. High intensity bright lamp inspection as per ASTM F523.

Additional Information

Icemos Technology Ltd